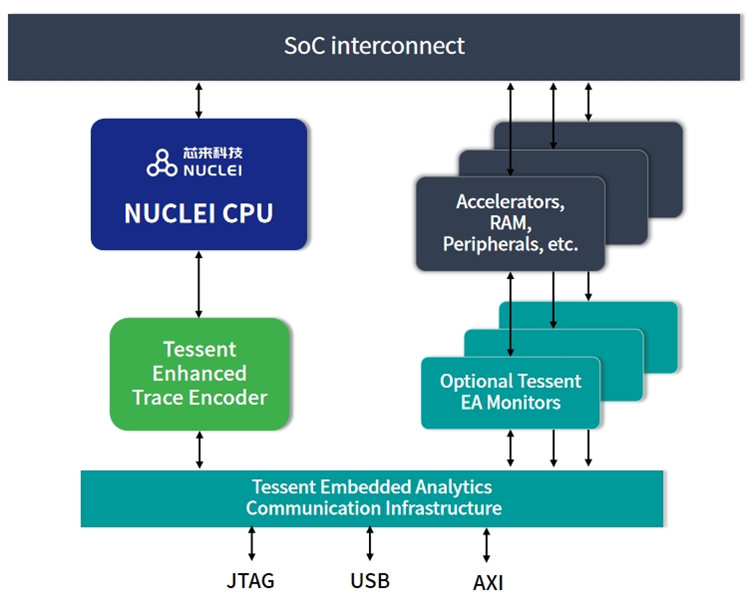

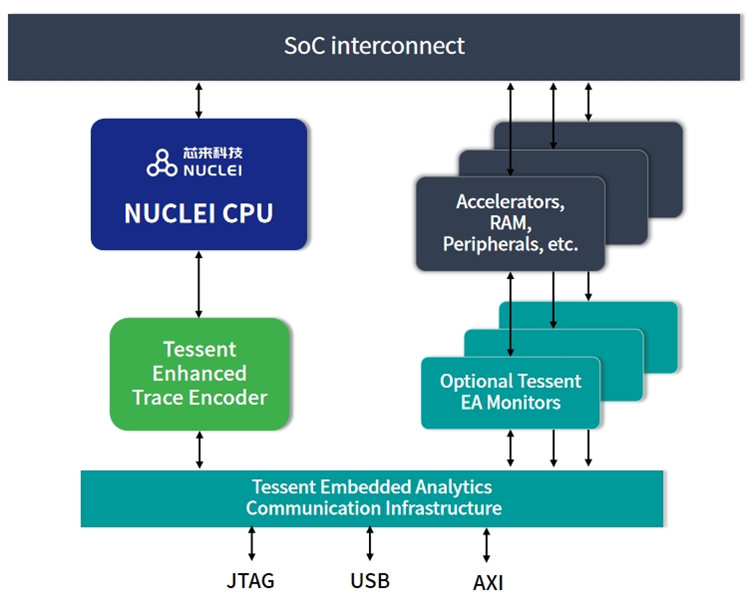

日,西门子EDA与芯来科技宣布达成战略合作:西门子EDA的Tessent Enhanced 必威官方网站 必威网址Trace Encoder增强型追踪编码器解决方案已全面支持芯来RISC-V处理器内核,该解决方案将为选择芯来科技RISC-V CPU IP的客户提供一种实时监控CPU程序执行的机制。它将在SoC层面对程序执行(指令跟踪)以及可选的加载和存储指令中的数据(数据跟踪)进行编码,以高度压缩的格式输出跟踪,使用户在复杂的异构设计中显著提高生产效率。这一合作旨在共同推动RISC-V生态系统的建设和发展,为全球半导体行业带来更多创新和机遇。

Tessent Enhanced Trace Encoder增强型追踪编码器解决方案是西门子EDA的Tessent Embedded Analytics嵌入式分析产品线成员产品。通过这一联合解决方案,开发人员可以有效地追踪和调试芯片和软件之间的问题,并能准确了解基于芯来RISC-V CPU IP的实时运行状态。Tessent Enhanced Trace Encoder增强型追踪编码器完全满足RISC-V基金会调试和追踪工作组(Debug and Trace Working Group)制定的标准规范,同时还支持自定义指令的调试跟踪,为用户提供了一个更为高效的调试工具环境,在复杂系统的开发必威平台 必威官方首页中能够显著提升的研发效率。

芯来科技拥有丰富的RISC-V CPU IP矩阵,覆盖从低功耗到高性能的各种应用需求,遍及5G通信、工业控制、人工智能、汽车电子、物联网、存储、MCU、网络安全等多个领域。芯来科技的RISC-V CPU IP具有高度可配置性,用户可以在上百个选项中根据实际需求选择最贴近下游应用的配置,并实现最大程度的优化。此次合作整合了RISC-V处理器IP集成和调试追踪工具,更进一步提高了客户芯片研发的效率。

芯来科技CEO彭剑英表示:芯来科技的RISC-V CPU IP具有业界最高的质量控制标准。为了提升用户的使用体验和优化客户SoC设计中的调试方案,我们需要一个像Tessent Enhanced Trace Encoder增强型追踪编码器这样的优质工具协助我们的下游客户进行开发工作,该工具的引入将能为我们的客户提供更为高效的调试和跟踪方案。”

“Tessent Embedded Analytics嵌入式分析工具可实现全系统实时调试和部署后的分析,从而帮助使用者产出高质量的、创新的产品,并将其快速推向市场。”西门子EDA Tessent部门副总裁兼总经理Ankur Gupta说道,“芯来科技作为中国大陆领先的RISC-V解决方案提供商,服务了大量的芯片客户,我们很高兴能够与其成为合作伙伴关系共同支持目标客户的芯片研发。”

芯来科技与西门子EDA此次合作的达成,将极大的提升RISC-V CPU IP的客户的研发效率,对RISC-V生态建设起到积极的推进作用。

立面测量是获取建筑立面数据和面貌,支撑城镇旧改工程、重点建筑保护、城市规划设计等事项的基础性工作。部分城镇建筑年代久远,项目缺少竣

在数字化浪潮的推动下,区块链与人工智能这两大前沿技术正携手并进,为企业数字化转型开辟了一条前所未有的道路。作为国内电子数据存证保全

2023年以来,随着光伏行业进入产能过剩及n型技术革新的双重周期,光伏行业陷入混沌期,在产业链价格持续下行的影响下,内卷、过剩、降价成

走进由浙江业丰建设有限公司承建的瑞安市安阳街道社区卫生必威平台 必威官方首页服务中心项目的建设工地,一场主题为奋进新时代,谱写新篇章的红色展览正在火热开

2024年度《亚洲银行家》奖项颁布近日,由国际权威财经机构《亚洲银行家》(The Asian Banker)主办的第 23 届中国未来金融峰会及中国奖

![]()

版权所有 本网本网商业快讯取消西门子EDA与芯来科技达成战略合作 共同推进RISC-V生态建设

近日,西门子EDA与芯来科技宣布达成战略合作:西门子EDA的Tessent Enhanced Trace Encoder增强型追踪编码器解决方案已全面支持芯来RISC-V处理器内核,该解决方案将为选择芯来科技RISC-V CPU IP的客户提供一种实时监控CPU程序执行的机制。它将在SoC层面对程序执行(指令跟踪)以及可选的加载和存储指令中的数据(数据跟踪)进行编码,以高度压缩的格式输出跟踪,使用户在复杂的异构设计中显著提高生产效率。这一合作旨在共同推动RISC-V生态系统的建设和发展,为全球半导体行业带来更多创新和机遇。

Tessent Enhanced Trace Encoder增强型追踪编码器解决方案是西门子EDA的Tessent Embedded Analytics嵌入式分析产品线成员产品。通过这一联合解决方案,开发人员可以有效地追踪和调试芯片和软件之间的问题,并能准确了解基于芯来RISC-V CPU IP的实时运行状态。Tessent Enhanced Trace Encoder增强型追踪编码器完全满足RISC-V基金会调试和追踪工作组(Debug and Trace Working Group)制定的标准规范,同时还支持自定义指令的调试跟踪,为用户提供了一个更为高效的调试工具环境,在复杂系统的开发中能够显著提升的研发效率。

芯来科技拥有丰富的RISC-V CPU IP矩阵,覆盖从低功耗到高性能的各种应用需求,遍及5G通信、工业控制、人工智能、汽车电子、物联网、存储、MCU、网络安全等多个领域。芯来科技的RISC-V CPU IP具有高度可配置性,用户可以在上百个选项中根据实际需求选择最贴近下游应用的配置,并实现最大程度的优化。此次合作整合了RISC-V处理器IP集成和调试追踪工具,更进一步提高了客户芯片研发的效率。

芯来科技CEO彭剑英表示:芯来科技的RISC-V CPU IP具有业界最高的质量控制标准。为了提升用户的使用体验和优化客户SoC设计中的调试方案,我们需要一个像Tessent Enhanced Trace Encoder增强型追踪编码器这样的优质工具协助我们的下游客户进行开发工作,该工具的引入将能为我们的客户提供更为高效的调试和跟踪方案。”

“Tessent Embedded Analytics嵌入式分析工具可实现全系统实时调试和部署后的分析,从而帮助使用者产出高质量的、创新的产品,并将其快速推向市场。”西门子EDA Tessent部门副总裁兼总经理Ankur Gupta说道,“芯来科技作为中国大陆领先的RISC-V解决方案提供商,服务了大量的芯片客户,我们很高兴能够与其成为合作伙伴关系共同支持目标客户的芯片研发。”

芯来科技与西门子EDA此次合作的达成,将极大的提升RISC-V CPU IP的客户的研发效率,对RISC-V生态建设起到积极的推进作用。